1. Introduction

Les oscillateurs à quartz génèrent des signaux d'horloge très stables, indispensables dans presque tous les systèmes électroniques, des simples circuits de microcontrôleur aux systèmes de transmission de données à haut débit.

Le signal de sortie d'un oscillateur doit être compatible avec la famille logique ou l'interface en aval. Au fil des décennies, différents standards de sortie ont été développés, chacun adapté aux exigences de son époque et de son application.

Ce document fournit un aperçu complet des sept types de signaux de sortie les plus courants dans les oscillateurs à quartz : CMOS, TTL, onde sinusoïdale écrêtée, sinusoïdale, LVPECL, LVDS et HCSL.

Pour chaque type, le développement historique, les caractéristiques électriques, la forme de signal typique ainsi que les domaines d'application préférés sont expliqués.

2. Développement historique

Le développement des types de signaux de sortie est étroitement lié à l'évolution de la technologie des semi-conducteurs et aux exigences croissantes en matière de fréquences d'horloge et d'intégrité du signal :

2.1 TTL (Logique Transistor-Transistor) – à partir d'env. 1964

Le TTL fut l'un des premiers standards logiques numériques largement répandus et fut introduit par Texas Instruments sous la série 7400. Les oscillateurs à sortie TTL fonctionnent avec une tension d'alimentation de 5 V et fournissent des plages de niveaux directement compatibles avec les portes TTL. Ce standard a façonné l'électronique numérique pendant des décennies et était le standard logique dominant jusqu'aux années 1990.

2.2 CMOS (Complementary Metal-Oxide-Semiconductor) – à partir d'env. 1968

La technologie CMOS, initialement développée par RCA, se caractérise par une consommation de courant de repos extrêmement faible. Les oscillateurs CMOS fournissent des signaux de sortie rail-à-rail, c'est-à-dire que la tension de sortie oscille presque exclusivement entre 0 V et VCC. Avec la miniaturisation croissante et la tendance à la baisse des tensions d'alimentation (3,3 V, 2,5 V, 1,8 V), la technologie CMOS est devenue la norme de sortie la plus répandue pour les oscillateurs à quartz.

2.3 Sinus – depuis les débuts de la technique des oscillateurs

Les signaux de sortie sinusoïdaux sont aussi anciens que la technologie des oscillateurs elle-même. Les oscillateurs à quartz oscillent physiquement de façon sinusoïdale ; toutes les autres formes de signal sont générées par les circuits en aval. Les signaux de sortie sinusoïdaux sont privilégiés dans les technologies haute fréquence, les instruments de mesure et le traitement analogique du signal car ils ne génèrent pas d'harmoniques.

2.4 Clipped Sine Wave – à partir d'env. années 1970

La sortie Clipped Sine Wave représente un compromis entre la sortie sinusoïdale et la sortie rectangulaire. Le signal sinusoïdal est limité (écrêté) aux crêtes, créant des fronts plus raides qu'un sinus pur mais moins d'harmoniques qu'un signal rectangulaire. Ce type de sortie était particulièrement utilisé dans les télécommunications et les applications haute fréquence plus anciennes. Les circuits Clipped Sine Wave sont encore principalement utilisés dans les TCXO aujourd'hui. Cette technologie permet de construire des TCXO nettement plus économes en énergie qu'avec la technologie CMOS. Les CSW-TCXO sont donc utilisés comme référence dans les appareils de navigation, les systèmes d'appel d'urgence et les passerelles. Partout où la portée du signal (radio) et un positionnement de haute précision sont nécessaires.

2.5 LVPECL (Low-Voltage Positive Emitter-Coupled Logic) – à partir d'env. années 1990

Avec le besoin de fréquences d'horloge toujours plus élevées dans les systèmes de réseau et de télécommunication, le LVPECL est apparu comme logique de sortie différentielle rapide. Le LVPECL est basé sur la technique ECL classique (Emitter-Coupled Logic), déjà développée dans les années 1960 pour les applications à haute vitesse, et l'adapte pour des tensions d'alimentation plus basses (3,3 V au lieu de -5,2 V). Le LVPECL offre des temps de commutation extrêmement courts et convient pour des fréquences bien au-delà de 1 GHz.

2.6 LVDS (Low-Voltage Differential Signaling) – à partir de 1994

Le LVDS a été introduit en 1994 comme standard ANSI/TIA/EIA-644 et optimise la transmission différentielle du signal pour une faible consommation et des débits de données élevés. La faible excursion de tension différentielle de seulement 350 mV permet une commutation rapide avec un rayonnement électromagnétique minimal. Le LVDS est aujourd'hui largement répandu dans les interfaces d'affichage, les liaisons de données série et le clocking FPGA.

2.7 HCSL (High-Speed Current Steering Logic) – à partir d'env. 2002

Le HCSL a été spécialement développé pour le standard PCI Express et est le standard d'horloge de référence depuis la première génération PCIe. Le PCI-SIG a spécifié le HCSL comme signal différentiel basé sur le mode courant avec une très faible excursion de tension, optimisé pour les horloges de référence de 100 MHz dans les systèmes PCIe. Le HCSL est aujourd'hui indispensable dans chaque PC, serveur et système embarqué avec interface PCIe.

3. aperçu des formes de signaux

Les diagrammes suivants montrent les courbes de signal idéalisées des sept types de sortie. Notez les différentes plages de tension et les amplitudes d'oscillation - elles sont déterminantes pour la compatibilité avec les récepteurs en aval.

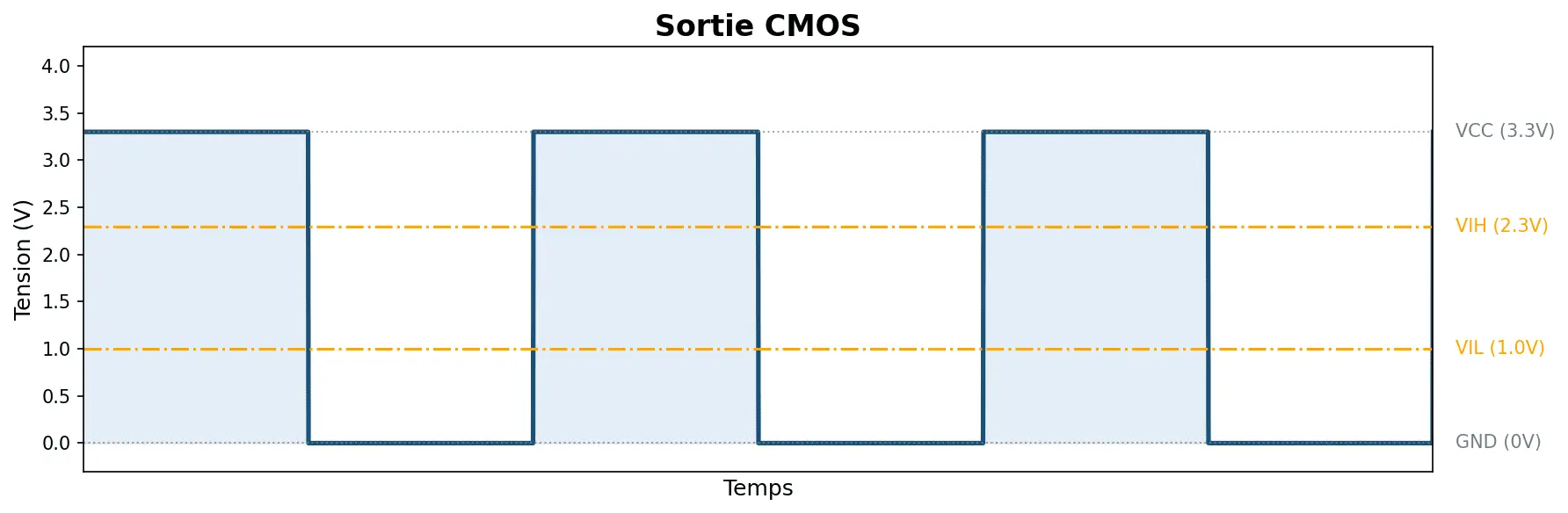

3.1 CMOS

Fig. 1 : Signal de sortie CMOS – Signal rectangulaire rail-to-rail entre 0 V et VCC (ici 3,3 V)

Le signal CMOS se caractérise par son excursion de tension complète entre GND et VCC. Les seuils d'entrée VIL et VIH se situent typiquement à 30 % et 70 % de VCC respectivement, garantissant une large marge de bruit. Les structures de driver de sortie symétriques (MOSFET canal P/canal N) permettent des temps de montée et de descente presque égaux.

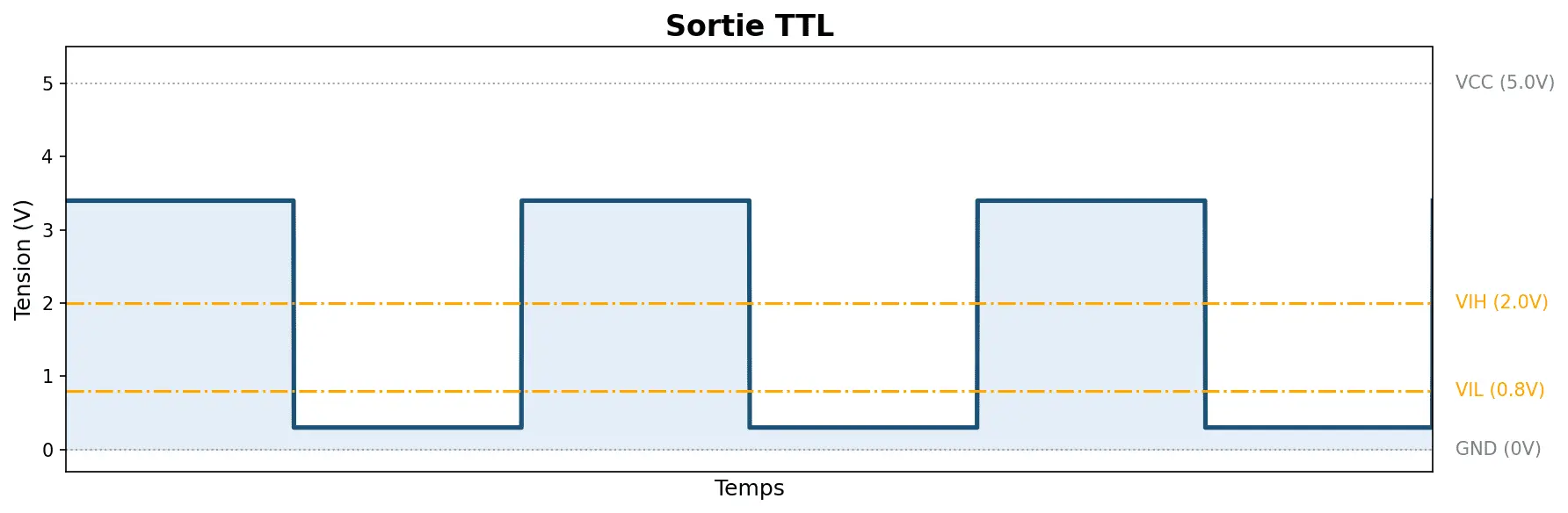

3.2 TTL

Fig. 2 : Signal de sortie TTL – VOH typiquement 3,4 V, VOL typiquement 0,3 V à 5 V d'alimentation

Contrairement aux sorties CMOS, les transistors TTL n'atteignent pas des niveaux de tension rail-à-rail. Le niveau haut (VOH) est typiquement de 3,4 V (minimum 2,4 V), et le niveau bas (VOL) est au maximum de 0,4 V. Les seuils asymétriques (VIL = 0,8 V, VIH = 2,0 V) résultent de l'architecture bipolaire du transistor. La plage dite « interdite » entre 0,8 V et 2,0 V ne doit pas être prise en compte en fonctionnement statique.

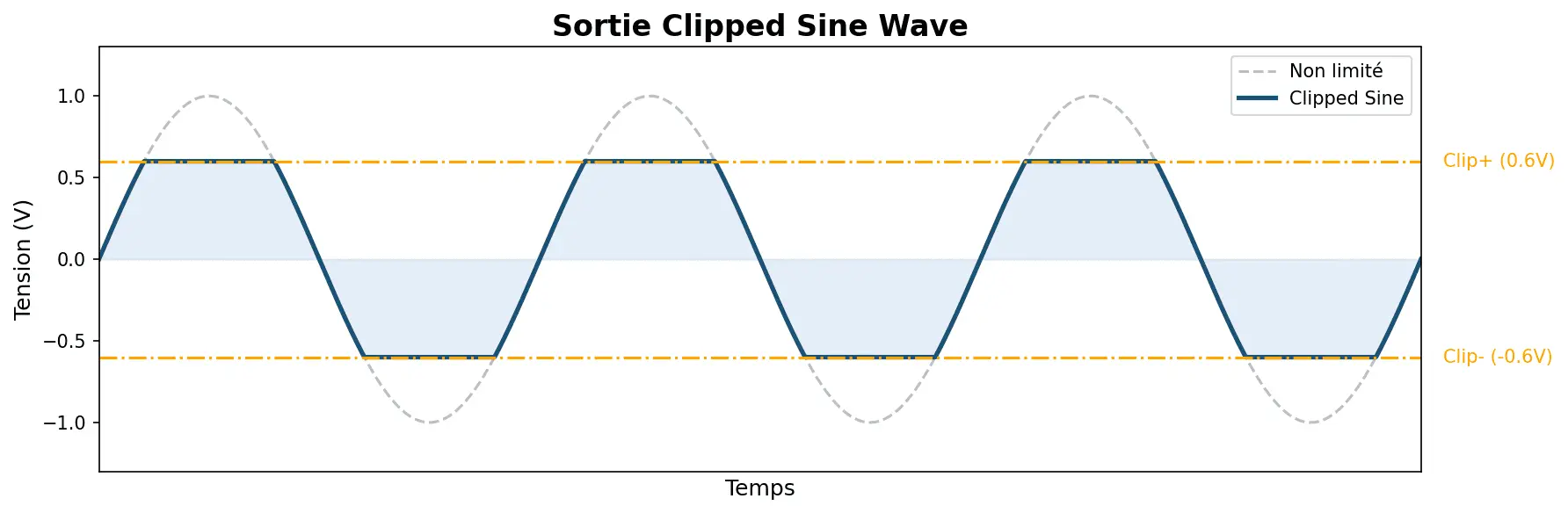

3.3 Clipped Sine Wave

Fig. 3 : Sortie Clipped Sine Wave – Signal sinusoïdal avec crêtes d'amplitude limitées

Avec la sortie Clipped Sine Wave, le signal sinusoïdal naturel du résonateur à quartz est limité à des seuils définis. La ligne en pointillés montre la forme sinusoïdale non écrêtée. L'écrêtage crée des passages par zéro plus raides qu'avec le sinus pur, facilitant l'attaque de la logique en aval, tandis que le contenu en harmoniques reste modéré.

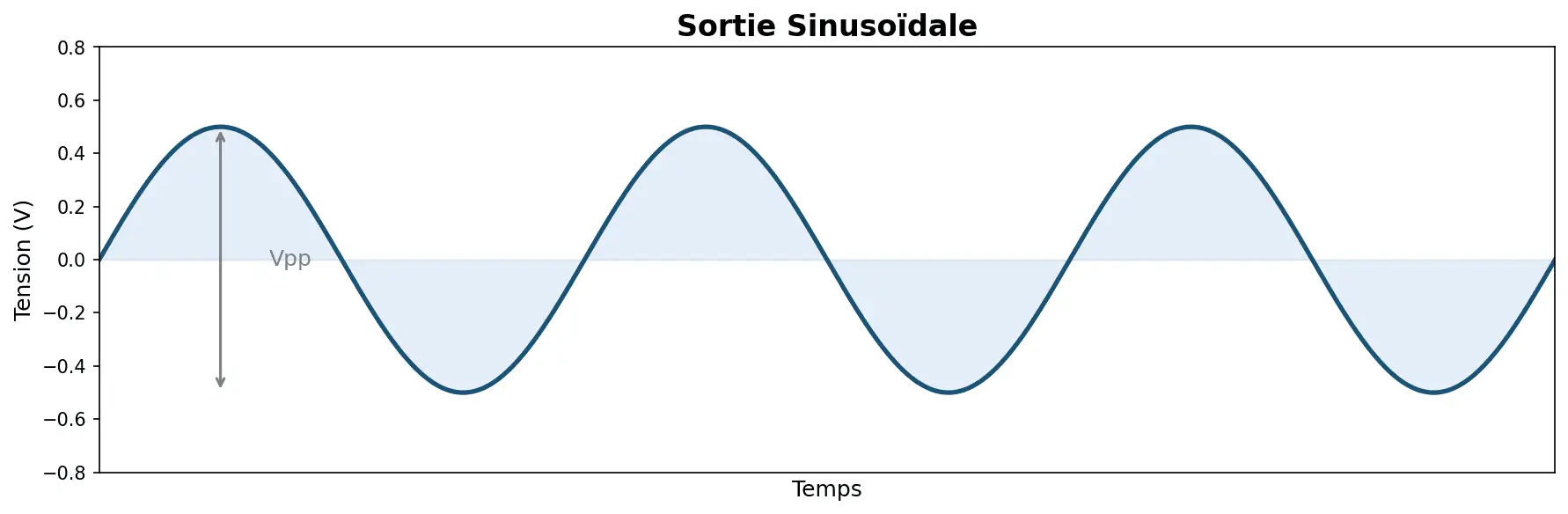

3.4 Sinus

Fig. 4 : Sortie sinusoïdale – Signal sinusoïdal pur avec tension crête-à-crête définie (Vpp)

La sortie sinusoïdale fournit le spectre le plus propre de toutes les formes de sortie : idéalement une seule raie spectrale à la fréquence fondamentale. L'amplitude est spécifiée en tension crête-à-crête (Vpp) ou en puissance en dBm. Les valeurs typiques sont de 0,5 à 1,0 Vpp ou de 0 à +13 dBm dans les systèmes 50 Ω.

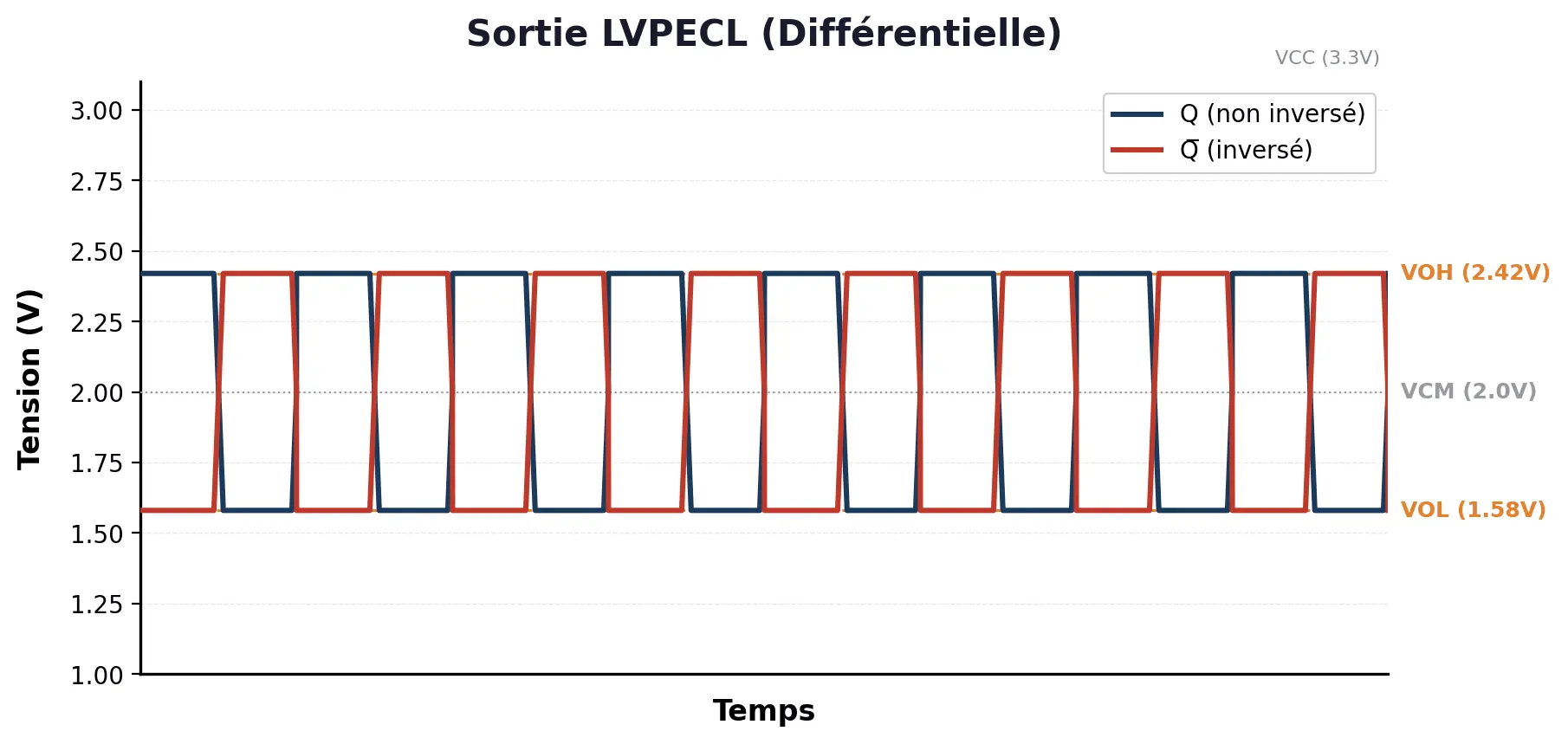

3.5 LVPECL

Fig. 5 : Sortie LVPECL – Signal différentiel avec env. 800 mV d'excursion totale autour de VCC–1,3 V

Le LVPECL utilise un routage de signal différentiel : deux sorties complémentaires (Q et Q̅) oscillent en opposition de phase autour d'un niveau de mode commun (VCM), typiquement à VCC–1,3 V. L'excursion de tension différentielle est d'env. 800 mV. L'architecture à source de courant permet des temps de commutation extrêmement rapides avec une tendance minimale au dépassement.

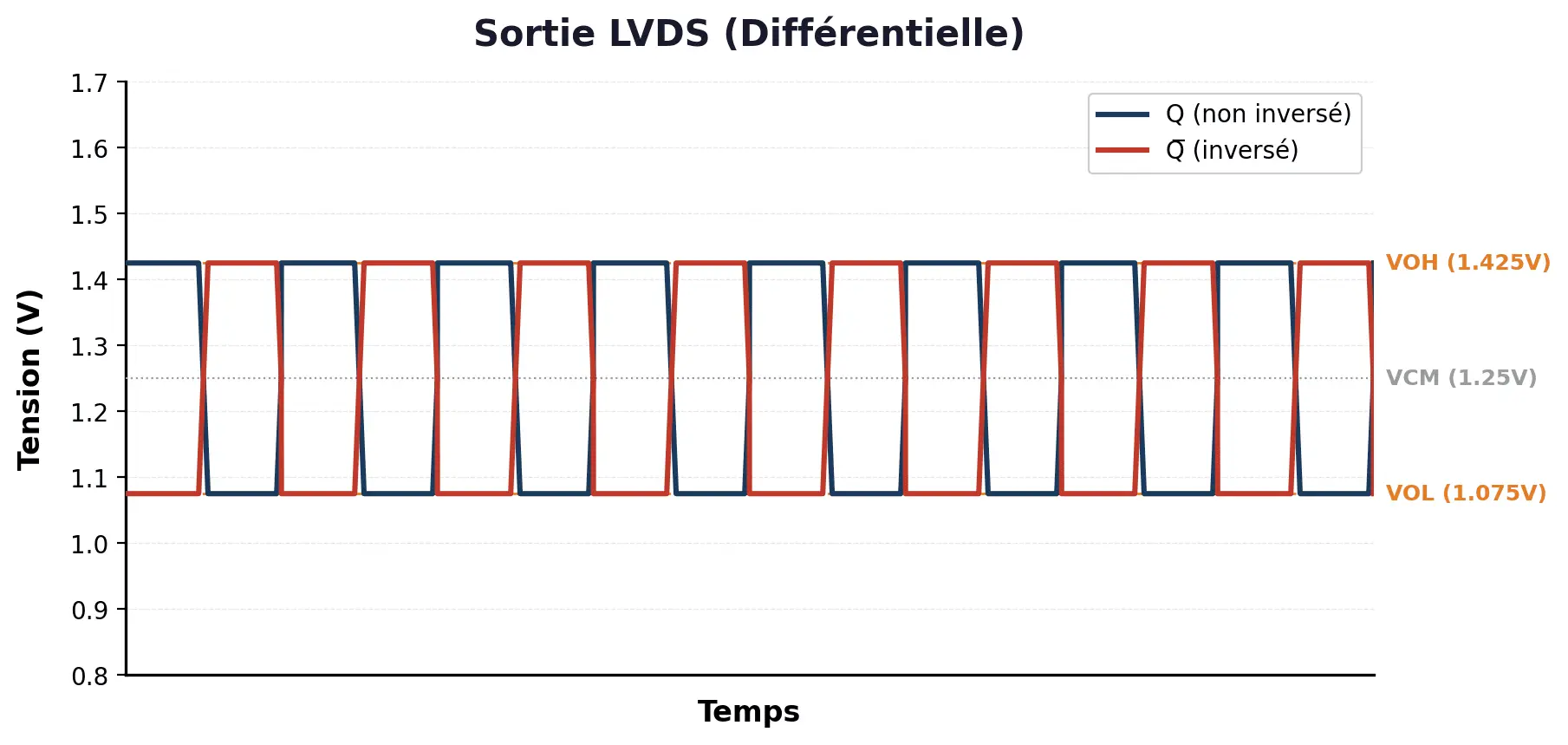

3.6 LVDS

Fig. 6 : Sortie LVDS – Signal différentiel avec seulement 350 mV d'excursion autour de 1,25 V de niveau de mode commun

Le LVDS se caractérise par son excursion de tension différentielle particulièrement faible de seulement 350 mV. Le niveau de mode commun est à 1,25 V. Grâce au driver piloté en courant (typiquement 3,5 mA) et à la terminaison 100 Ω, une haute intégrité du signal est obtenue avec une consommation minimale. La faible amplitude minimise le rayonnement électromagnétique.

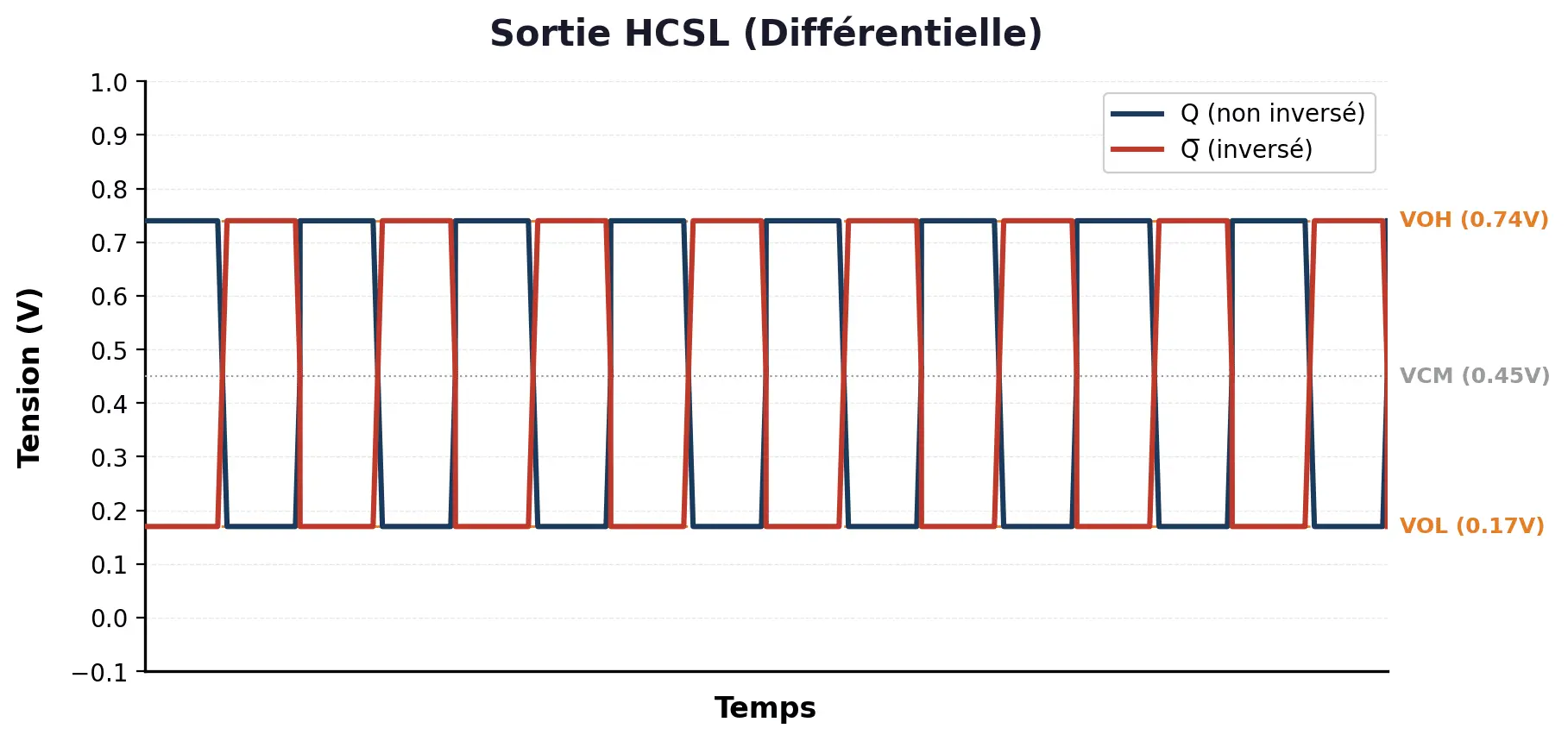

3.7 HCSL

Fig. 7 : Sortie HCSL – Signal différentiel en mode courant pour les horloges de référence PCIe

Le HCSL fonctionne avec une très faible excursion de tension : VOH est typiquement de 0,74 V et VOL de 0,17 V, résultant en un niveau de mode commun d'env. 0,45 V. L'architecture de pilotage en courant est spécialement optimisée pour les exigences de la spécification PCIe et permet une adaptation d'impédance précise via des terminaisons 50 Ω vers la masse.

4. Comparaison des signaux de sortie

Le tableau suivant résume les propriétés essentielles des sept types de sortie :

Type | Type de signal | VCC (V) | VOH/ VOL (V) | Diff. Course | Fréq. max. env. | Application typique |

| CMOS | Single- Ended | 1,8-5,0 | VCC/ 0 | - | ~285 MHz | Microcontrôleurs, FPGA, technique numérique générale |

| TTL | Single- Ended | 1,8-5,0 | 3,4/ 0,3 | - | ~150 MHz | Systèmes patrimoniaux, commandes industrielles |

| Clipped Sine | Single- Ended | 1,8/2,5/3,3 | variable | - | ~200 MHz | Télécommunications, applications HF |

| Sinus | Single- Ended | 3,3/5,0/12 | variable | - | >1 GHz | Technique HF, appareils de mesure, synthèse de fréquence |

| LVPECL | Différentiel | 2,5/3,3 | ~2,4/ ~1,6 | ~800 mV | >3 GHz | Équipement réseau, SONET/SDH, clocking haute vitesse |

| LVDS | Différentiel | 2,5/3,3 | ~1,43/ ~1,07 | 350 mV | >1 GHz | Interfaces d'affichage, liens série, clocking FPGA |

| HCSL | Différentiel | 3,3 | 0,74/ 0,17 | ~570 mV | ~200 MHz | Horloge de référence PCI Express (100 MHz) |

5. Différences essentielles en détail

5.1 Single-Ended vs. Différentiel

La différence la plus fondamentale entre les types de sortie est le routage du signal. CMOS, TTL, Clipped Sine Wave et Sinus sont des signaux single-ended – ils sont référencés à une masse commune. LVPECL, LVDS et HCSL en revanche sont des signaux différentiels avec deux lignes complémentaires. Les signaux différentiels offrent des avantages décisifs aux fréquences plus élevées : ils suppriment les perturbations de mode commun, permettent des excursions de tension plus faibles et ainsi des temps de commutation plus rapides avec moins de rayonnement électromagnétique.

5.2 Excursion de tension et marge de bruit

Le CMOS offre la plus grande excursion de tension absolue avec sa sortie rail-to-rail et donc la meilleure marge de bruit statique. Le TTL a une marge de bruit plus limitée en raison de ses niveaux asymétriques. Les standards différentiels (LVPECL, LVDS, HCSL) compensent leurs excursions de tension plus faibles par la réjection de mode commun de la transmission différentielle, ce qui les rend souvent plus fiables dans les environnements perturbés que les signaux single-ended.

5.3 Consommation de courant

Les oscillateurs CMOS ne consomment pratiquement aucun courant à l'état statique ; la consommation augmente proportionnellement avec la fréquence (dissipation dynamique). Le TTL a une consommation de courant de repos constamment plus élevée en raison de l'architecture bipolaire. Le LVPECL nécessite des résistances de terminaison externes et a la consommation la plus élevée des standards différentiels. Le LVDS est connu pour sa faible consommation (typiquement 3,5 mA de courant de driver). Le HCSL se situe entre le LVDS et le LVPECL en termes de consommation.

5.4 Plage de fréquences et domaines d'application

Pour des fréquences allant jusqu'à environ 200 MHz, les oscillateurs CMOS sont généralement privilégiés en raison de leur polyvalence, de la simplicité de leur conception et de leur large disponibilité. Au-delà de 200 MHz environ, les sorties différentielles sont recommandées. LVPECL offre les fréquences les plus élevées (> 3 GHz) et est utilisé dans les équipements de réseau et de télécommunications. LVDS couvre une large gamme de fréquences moyennes et est particulièrement répandu dans les applications FPGA et d'affichage. HCSL est optimisé pour son application spécifique : l'horloge de référence à 100 MHz pour PCI Express.

5.5 Terminaison et complexité du circuit

Les sorties CMOS et TTL ne nécessitent généralement pas de terminaison externe pour de courtes longueurs de piste – cela les rend particulièrement simples d'utilisation. Le LVPECL requiert impérativement des résistances de terminaison externes (typiquement : terminaison Thévenin vers VCC–2 V ou résistances vers la masse), ce qui augmente la complexité du circuit. Le LVDS est terminé par défaut avec une résistance différentielle de 100 Ω au récepteur. Le HCSL utilise des résistances de 50 Ω vers la masse à chaque sortie.

6. Dépassement dans les signaux de sortie d'oscillateur

6.1 Qu'est-ce que le dépassement ?

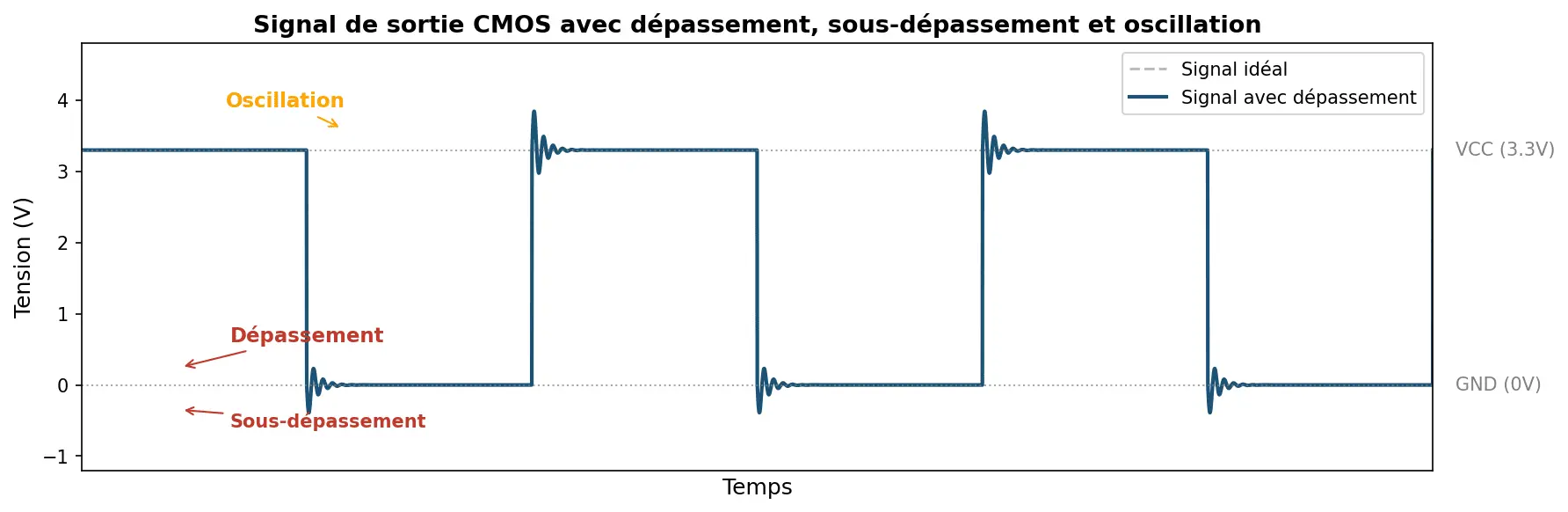

Les surtensions et les sous-tensions sont de brèves variations de tension qui se produisent lors de commutations rapides. Sur un front montant, la tension dépasse brièvement VCC (surtension), tandis que sur un front descendant, elle chute légèrement en dessous de GND (sous-tension). Ces surtensions sont souvent suivies d'oscillations amorties appelées « rémanence ».

La cause réside dans la combinaison des fronts de commutation très raides du driver de sortie et des inductances et capacités parasites de la piste, du boîtier et de la capacité de charge. Physiquement, un circuit résonant se forme à partir de l'inductance de la ligne et de la capacité d'entrée du récepteur. Plus le front de commutation est raide et plus la piste est longue, plus le dépassement est prononcé.

Fig. 8 : Signal de sortie CMOS avec dépassement – Overshoot au-dessus de VCC, undershoot en dessous de GND et ringing consécutif

6.2 Pourquoi le dépassement est-il problématique ?

Les dépassements au-delà de VCC ou en dessous de GND peuvent polariser en direct les diodes de protection ESD du circuit récepteur, générant des courants parasites. Dans le pire des cas, cela peut conduire à un latch-up – un flux de courant incontrôlé à travers les structures thyristor parasites dans le circuit CMOS, pouvant détruire le composant. Un ringing important peut également provoquer des déclenchements multiples aux entrées d'horloge lorsque la tension croise le seuil de commutation plusieurs fois, entraînant un comportement système erroné.

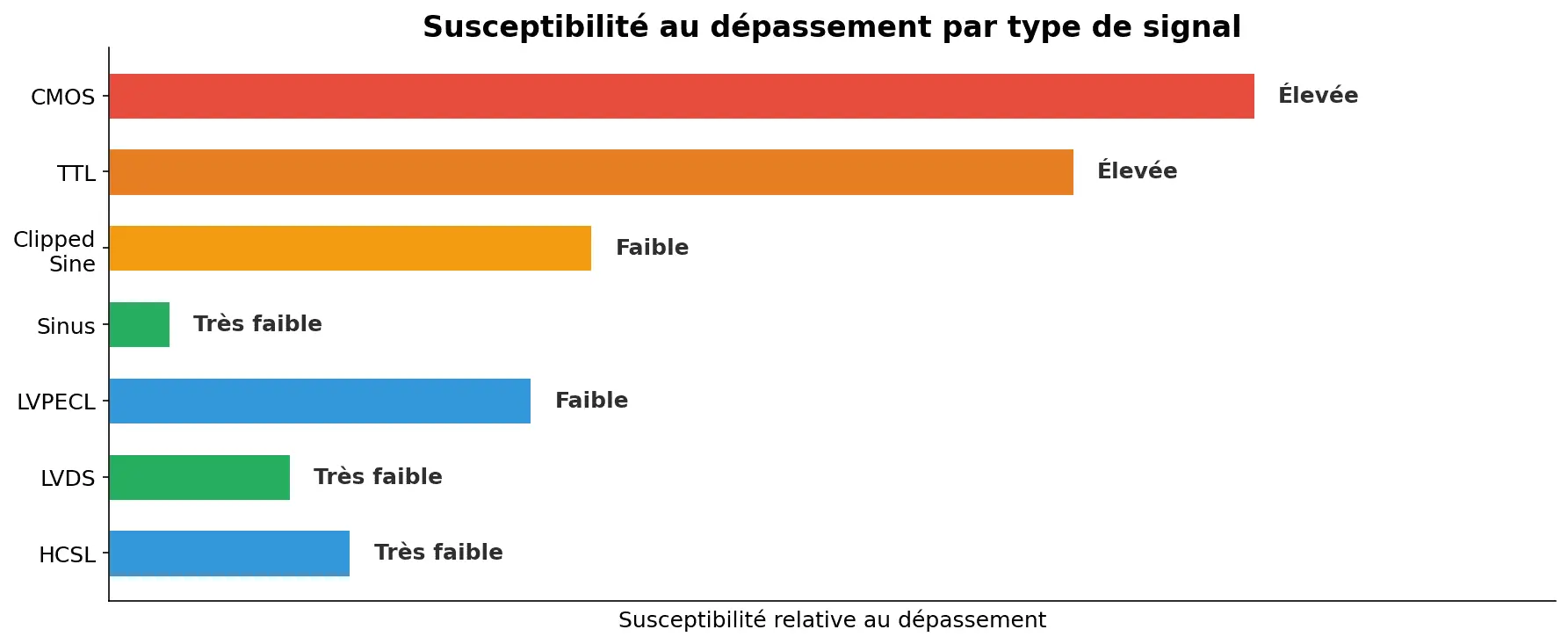

6.3 Comparaison : dépassement par type de signal

La susceptibilité au dépassement diffère considérablement entre les différents types de sortie. Le graphique suivant montre la susceptibilité relative en comparaison :

6.4 Dépassement dans les signaux single-ended

CMOS: Le plus affecté. Les drivers MOSFET symétriques canal P/canal N génèrent des fronts très raides qui, combinés aux inductances de piste, provoquent des dépassements prononcés. Avec les oscillateurs CMOS basse tension modernes (1,8 V) en particulier, les dépassements peuvent être significatifs par rapport à la tension d'alimentation.

TTL: Également susceptible, mais pour des raisons légèrement différentes. L'étage de sortie asymétrique totem-pole génère un bref pic de courant sur le front montant lorsque les deux transistors conduisent simultanément (cross-conduction). Les fronts typiquement un peu plus lents par rapport au CMOS moderne atténuent légèrement le problème.

Clipped Sine Wave: Nettement moins susceptible. Les crêtes d'amplitude limitées et les fronts comparativement doux produisent beaucoup moins d'énergie haute fréquence susceptible d'exciter des réflexions et du ringing. L'écrêtage agit comme un limiteur d'amplitude naturel qui supprime le dépassement déjà dans le signal.

Signal sinusoidal: Pratiquement insensible au dépassement classique. L’absence de transitions abruptes dans le signal évite la génération d’impulsions d’énergie à large bande susceptibles d’exciter des résonances de ligne. Toutefois, des désadaptations d’impédance peuvent engendrer des ondes stationnaires et des réflexions modifiant l’amplitude du signal en certains points. Ce phénomène est maîtrisé par une terminaison RF classique (50 Ω ou 75 Ω).

6.5 Dépassement dans les signaux différentiels

LVPECL: Intrinsèquement bien supprimé grâce à l'étage de sortie à source de courant. Le pilotage en courant limite naturellement la pente maximale des fronts. Avec une terminaison insuffisante, des réflexions peuvent néanmoins survenir car le LVPECL fonctionne à de très hautes fréquences. Le circuit Thévenin ou suiveur d'émetteur correct est ici décisif – non pas principalement à cause du dépassement, mais pour assurer le point de fonctionnement correct et éviter les réflexions.

LVDS: Très robuste de par sa conception. Le driver piloté en courant fournit un courant constant de typiquement 3,5 mA dans la terminaison différentielle 100 Ω, limitant physiquement l'excursion de tension. Même avec des discontinuités d'impédance, les réflexions restent faibles car la faible excursion de tension de seulement 350 mV fournit peu d'énergie pour les perturbations. Le LVDS est l'un des standards les plus tolérants en matière d'intégrité du signal.

HCSL: Se comporte de manière similaire au LVDS grâce à l'architecture basée sur le courant. La très faible excursion de tension et la terminaison 50 Ω vers la masse assurent une adaptation d'impédance propre. Dans la spécification PCIe, le dépassement admissible est explicitement défini et étroitement toléré, de sorte que les oscillateurs conformes HCSL respectent ces exigences de manière inhérente.

6.6 Contre-mesures pour le contrôle du dépassement

La mesure la plus efficace pour les signaux single-ended (notamment CMOS et TTL) est une résistance série directement à la sortie de l'oscillateur, typiquement dans la plage de 22 à 47 Ω. Cette résistance forme avec l'impédance de la piste un diviseur de tension qui amortit le front et absorbe les réflexions. La valeur optimale résulte de la différence entre l'impédance de la piste et l'impédance de sortie du driver.

De plus, des pistes courtes à impédance contrôlée, la minimisation des vias sur la ligne d'horloge, un plan de masse continu sous la ligne de signal ainsi que des condensateurs de découplage suffisants près de l'oscillateur (typiquement 100 nF céramique plus 10 µF) sont utiles. Certains fabricants d'oscillateurs CMOS proposent également des modèles avec contrôle de la pente des fronts (Slew Rate Control) qui atténuent le problème dès le driver.

Pour les signaux différentiels (LVPECL, LVDS, HCSL), la terminaison correcte et conforme aux spécifications est la mesure la plus importante. De plus, les deux lignes d'une paire différentielle doivent toujours être routées avec une longueur égale et un couplage étroit pour minimiser le skew (différences de temps de propagation) et maintenir la réjection de mode commun.

7. Aide à la décision

Le choix du bon type de sortie dépend essentiellement de quatre facteurs : la fréquence d'horloge requise, la famille logique du récepteur, le budget de puissance disponible et les exigences en matière d'intégrité du signal.

Cas d'application | Recommandation |

| Technique numérique générale, µC, FPGA I/O (jusqu'à ~200 MHz) | CMOS – Solution la plus simple et la plus économique, rail-to-rail, disponibilité la plus large, flexible en tension d'alimentation (1,8–5,0 V) |

| Systèmes 5V Legacy, commandes industrielles | TTL – Directement compatible avec les anciennes familles logiques 5V ; de plus en plus remplacé par le CMOS avec alimentation 5V |

| Applications HF, circuits à transformateur | Clipped Sine Wave ou Sinus – Un contenu harmonique plus faible réduit les problèmes CEM et permet une synthèse de fréquence précise |

| Équipement de réseau à haut débit (>622 MHz) | LVPECL – Vitesse de commutation la plus élevée, idéal pour SONET/SDH, Ethernet PHY et horloges backplane |

| Clocking FPGA, transmission de données série, interfaces d'affichage | LVDS – Compromis optimal entre vitesse, consommation et comportement CEM |

| Horloge de référence PCI Express | HCSL – Seul standard d'horloge spécifié par le PCI-SIG pour les systèmes PCIe |